커패시터가 있는 전기 회로

커패시터가 있는 전기 회로에는 전기 에너지원과 개별 커패시터가 포함됩니다. 커패시터는 유전층으로 분리된 임의의 형태의 두 도체 시스템입니다. 커패시터의 클램프를 일정한 전압 U로 전기 에너지 원에 연결하면 플레이트 중 하나에 + Q가 축적되고 다른 플레이트에는 -Q가 축적됩니다.

커패시터가 있는 전기 회로에는 전기 에너지원과 개별 커패시터가 포함됩니다. 커패시터는 유전층으로 분리된 임의의 형태의 두 도체 시스템입니다. 커패시터의 클램프를 일정한 전압 U로 전기 에너지 원에 연결하면 플레이트 중 하나에 + Q가 축적되고 다른 플레이트에는 -Q가 축적됩니다.

이러한 전하의 크기는 전압 U에 정비례하며 공식에 의해 결정됩니다.

큐 = 씨 ∙ 유,

여기서 C는 패럿(F) 단위로 측정된 커패시터의 커패시턴스입니다.

커패시터의 용량 값은 플레이트 중 하나의 전하 대 플레이트 사이의 전압의 비율, 즉 C = Q / U,

커패시터의 용량은 판의 모양, 치수, 상호 배열 및 판 사이의 매체의 유전 상수에 따라 다릅니다.

마이크로 패럿으로 표현되는 플랫 커패시터의 커패시턴스는 다음 공식에 의해 결정됩니다.

C = ((ε0 ∙ εr ∙ S) / d) ∙ 106,

여기서 ε0은 진공의 절대 유전 상수, εr은 판 사이의 매체의 상대 유전 상수, S는 판의 면적, m2, d는 판 사이의 거리, m입니다.

진공의 절대 유전 상수는 상수 ε0 = 8.855 ∙ 10-12 F/m입니다.

전압 U에서 플랫 커패시터의 플레이트 사이의 전계 강도 E의 크기는 공식 E = U / d에 의해 결정됩니다.

SI(International System of Units)에서 전계 강도의 단위는 미터당 볼트(V/m)입니다.

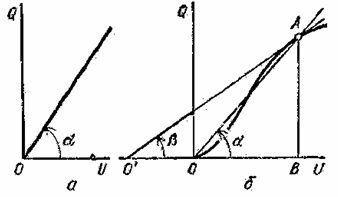

쌀. 1. 커패시터의 펜던트 -볼트 특성: a — 선형, b — 비선형

커패시터 플레이트 사이에 위치한 매체의 상대 투자율이 전계의 크기에 의존하지 않는 경우 커패시터의 커패시턴스는 단자의 전압 크기와 쿨롱 볼트 특성 Q에 의존하지 않습니다. = F(U)는 선형입니다(그림 1, a).

상대 투자율이 전기장의 강도에 따라 달라지는 강유전성 유전체가 있는 커패시터는 쿨롱 전압의 비선형 특성을 갖습니다(그림 1, b).

이러한 비선형 커패시터 또는 배리콘에서 쿨롱 특성의 각 지점, 예를 들어 지점 A는 정적 정전 용량 Cst = Q / U = (mQ ∙ BA) / (mU ∙ OB) = mC ∙ tan α 및 차동 커패시턴스 Cdiff = dQ / dU = (mQ ∙ BA) / (mU ∙ O'B) = mC ∙ tanβ, 여기서 mC는 전하 및 전압에 대해 각각 취한 스케일 mQ 및 mU에 따른 계수입니다.

각 커패시터는 용량 값뿐만 아니라 작동 전압 Urab 값으로도 특징지어지며 결과적인 전계 강도가 절연 내력보다 작도록 취합니다.절연 강도는 절연 특성의 파괴 및 손실과 함께 절연 파괴가 시작되는 최저 전압 값에 의해 결정됩니다.

유전체는 전기적 강도뿐만 아니라 약 1010 ~ 1020 Ω • cm 범위의 매우 큰 벌크 저항 ρV를 특징으로 하는 반면, 금속의 경우 10-6 ~ 10-4 Ω • 참조

또한 유전체의 경우 표면 누설 전류에 대한 저항을 특성화하는 비표면 저항 ρS의 개념이 도입되었습니다. 일부 유전체의 경우 이 값은 중요하지 않으므로 파손되지 않지만 표면의 전기 방전에 의해 차단됩니다.

다중 체인 전기 회로에 포함된 개별 커패시터의 단자에서 전압의 크기를 계산하기 위해 전기 방정식을 사용하는 주어진 EMF 소스에서 유사한 Kirchhoff의 법칙 방정식 직류 회로용.

따라서 커패시터가 있는 다중 체인 전기 회로의 각 노드에 대해 전기량 보존 법칙 ∑Q = Q0이 정당화되어 한 노드에 연결된 커패시터 플레이트의 대수적 전하 합은 다음과 같습니다. 서로 연결되기 전의 요금의 대수적 합계와 같습니다. 커패시터 판에 예비 전하가 없을 때 동일한 방정식은 ∑Q = 0의 형식을 갖습니다.

커패시터가 있는 전기 회로의 모든 회로에 대해 등식 ∑E = ∑Q / C가 참이며, 이는 회로에서 emf의 대수적 합이 포함된 커패시터 단자의 전압의 대수적 합과 같다는 것을 나타냅니다. 이 회로에서.

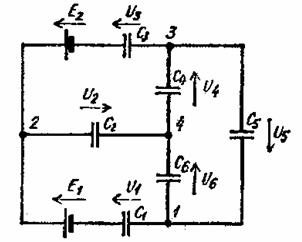

쌀. 2.커패시터가 있는 다중 회로 전기 회로

따라서 2개의 전기 에너지 소스와 초기 제로 전하를 갖는 6개의 커패시터가 있는 다중 회로 전기 회로에서 세 개의 독립 노드 1, 2, 3에 대한 전기량 보존 Q1 + Q6-Q5 = 0, -Q1-Q2-Q3 = 0, Q3-Q4 + Q5 = 0의 세 가지 방정식을 얻습니다.

세 개의 독립 회로 1—2—4—1, 2—3—4—2, 1—4—3—1에 대한 추가 방정식은 시계 방향으로 둘러쌀 때 형식 E1 = Q1 / C1 + Q2 / C2 -Q6 / C6, -E2 = -Q3 / C3 -Q4 / C4 -Q2 / C2, 0 = Q6 / C6 + Q4 / C4 + Q5 / C5.

6개 선형 방정식 시스템의 솔루션을 사용하면 각 커패시터 Qi의 전하량을 결정하고 Ui = Qi / Ci 공식으로 단자 Ui에서 전압을 찾을 수 있습니다.

마이너스 부호로 값을 구한 응력 Ui의 실제 방향은 방정식을 작성할 때 원래 가정한 것과 반대입니다.

커패시터가 있는 다중 체인 전기 회로를 계산할 때 델타에 연결된 커패시터 C12, C23, C31을 동등한 3점 스타에 연결된 커패시터 C1, C2, C3로 교체하는 것이 때때로 유용합니다.

이 경우 필요한 전력은 C1 = C12 + C31 + (C12 ∙ C31) / C23, C2 = C23 + C12 + (C23 ∙ C12) / C31, C3 = C31 + C23 + (C31 ∙ C23) ) / C12.

역변환에서 C12 = (C1 ∙ C2) / (C1 + C2 + C3), C23 = (C2 ∙ C3) / (C1 + C2 + C3), C31 = (C3 ∙ C1) / ( C1 + C2 + C3).

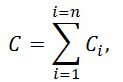

병렬로 연결된 커패시터 C1, C2, …, Cn은 단일 커패시터로 대체 가능

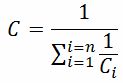

그리고 그들이 직렬로 연결될 때 — 용량이 다음과 같은 커패시터

회로에 포함 된 커패시터에 상당한 전기 전도도를 가진 유전체가 있으면 그러한 회로에 작은 전류가 나타나며 그 값은 직류 회로를 계산할 때 채택되는 일반적인 방법과 각 단자의 전압에 의해 결정됩니다 정상 상태의 커패시터는 공식에 의해 발견됩니다

우이 = 리 ∙ 이이,

여기서 Ri는 i번째 커패시터의 유전체층의 전기 저항이고 Ii는 동일한 커패시터의 전류입니다.

이 항목을 참조하십시오. 커패시터 충전 및 방전