앤티 앨리어싱 필터 및 전압 안정기

평활화 필터는 정류된 전압 리플을 줄이기 위해 설계되었습니다. 리플 스무딩은 스무딩 계수 q로 평가됩니다.

평활화 필터는 정류된 전압 리플을 줄이기 위해 설계되었습니다. 리플 스무딩은 스무딩 계수 q로 평가됩니다.

스무딩 필터의 주요 요소는 커패시터, 인덕터 직류와 교류에 대해 저항이 다른 트랜지스터.

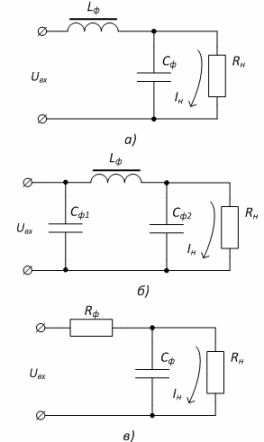

필터 소자의 유형에 따라 용량성, 유도성 및 전자식 필터로 구분됩니다. 필터링 링크 수에 따라 필터는 단일 링크와 다중 링크로 나뉩니다.

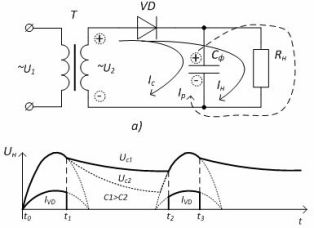

용량성 필터는 부하 저항 Rn과 병렬로 연결된 대용량 커패시터입니다. 커패시터는 DC 저항이 높고 AC 저항이 낮습니다. 반파 정류기 회로의 예에서 필터의 작동을 고려해 봅시다 (그림 1, a).

그림 1 - 용량성 필터가 있는 단상 반파 정류기: a) 회로 b) 작동 타이밍 다이어그램

양의 반파가 시간 간격 t0 — t1(그림 2.63, b)에 흐르면 부하 전류(다이오드 전류)와 커패시터 충전 전류가 흐릅니다.커패시터가 충전되고 시간 t1에서 커패시터의 전압이 2차 권선의 전압 강하를 초과합니다. 다이오드가 닫히고 시간 간격 t1에서 t2 부하의 전류는 커패시터의 방전에 의해 제공됩니다. 체. 부하의 전류는 지속적으로 흐르므로 정류 전압의 리플이 크게 줄어 듭니다.

커패시터 Cf의 커패시턴스가 클수록 여기가 작아집니다. 이것은 커패시터의 방전 시간(방전 시간 상수 τ = СfRн)에 의해 결정됩니다. τ> 10에서 스무딩 계수는 공식 q = 2π fc m Cf Rn에 의해 결정됩니다. 여기서 fc는 네트워크의 주파수이고 m은 정류 전압의 반주기 수입니다.

낮은 부하 전력에서 고저항 RH 부하 저항기가 있는 용량성 필터를 사용하는 것이 좋습니다.

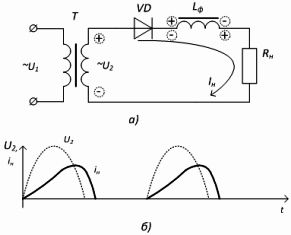

유도 필터(초크) Rn과 직렬로 연결됩니다(그림 3, a). 인덕턴스는 DC 저항이 낮고 AC 저항이 높습니다. 리플 스무딩은 처음에는 전류가 증가하는 것을 방지한 다음 감소를 지원하는 자체 유도 현상을 기반으로 합니다(그림 2, b).

그림 2 - 유도 필터가 있는 단상 반파 정류기: a) 회로, b) 작동 타이밍 다이어그램

유도 필터는 중간 및 고전력 정류기, 즉 큰 부하 전류로 작동하는 정류기에서 사용됩니다.

스무딩 계수는 다음 공식에 의해 결정됩니다. q = 2π fs m Lf / Rn

용량 성 및 유도 성 필터의 작동은 네트워크에서 소비되는 전류가 흐르는 동안 커패시터와 인덕터가 에너지를 저장하고 네트워크에서 전류가 없거나 감소하면 요소가 부하의 전류(전압)를 유지하면서 저장된 에너지를 차단합니다.

다중 접합 필터는 커패시터와 인덕터 모두의 평활 특성을 사용합니다. 부하 저항의 저항이 수 kOhm 인 저전력 정류기에서는 초크 Lf 대신 저항 Rf가 포함되어 필터의 질량과 크기를 크게 줄입니다.

그림 3은 LC 및 RC 래더 필터의 유형을 보여줍니다.

그림 3 - 다중 접합 필터: a) L자형 LC, b) U자형 LC, c) RC 필터

안정기는 주전원 전압의 변동 및 부하에서 소비되는 전류의 변화 중에 부하의 정전압(전류)을 안정화하도록 설계되었습니다.

안정기는 전압 및 전류 안정기와 파라 메트릭 및 보상 안정기로 나뉩니다. 출력 전압의 안정성은 안정화 계수 Kst로 평가됩니다.

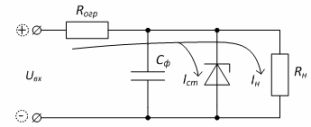

비선형 특성을 가진 요소 인 반도체 제너 다이오드를 사용하는 파라 메트릭 스태빌라이저 제너 다이오드의 전압은 장치를 통한 역 전류의 상당한 변화로 거의 일정합니다.

파라메트릭 스태빌라이저 회로는 그림 4에 나와 있습니다. 입력 전압 UBX는 제한 저항 Rlim과 병렬 연결된 제너 다이오드 VD 및 부하 저항 Rn 사이에 분배됩니다.

그림 4 - 파라메트릭 스태빌라이저

입력 전압이 증가함에 따라 제너 다이오드를 통과하는 전류가 증가합니다. 즉, 제한 저항을 통과하는 전류가 증가하고 더 큰 전압 강하가 발생하며 부하 전압은 변경되지 않습니다.

파라메트릭 스태빌라이저의 Kst는 20-50 정도입니다. 이러한 유형의 안정기의 단점은 낮은 안정화 전류와 낮은 효율입니다.

파라메트릭 스태빌라이저는 부하 전류가 작을 때(수백 밀리암페어 이하) 보조 전압 소스로 사용됩니다.

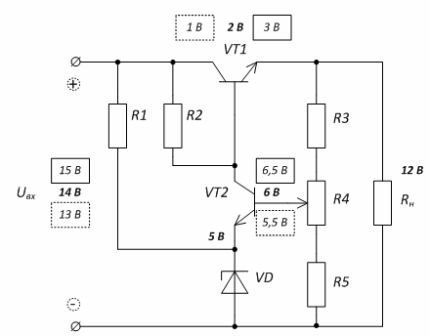

보상 안정기는 트랜지스터의 가변 저항을 제한 저항으로 사용합니다. 입력 전압이 증가하면 트랜지스터의 저항도 증가하고 그에 따라 전압이 감소하면 저항도 감소합니다. 이 경우 부하의 전압은 변경되지 않습니다.

트랜지스터의 안정기 회로는 그림 5에 나와 있습니다. 출력 전압 URn을 조절하는 원리는 조절 트랜지스터 VT1의 전도도 변화를 기반으로합니다.

그림 5 - 보상 전압 조정기의 개략도

전압 비교 회로와 DC 증폭기는 트랜지스터 VT2에 조립됩니다. 측정 회로 R3, R4, R5는 기본 회로에 포함되어 있고 기준 전압 소스 R1VD는 이미 터 회로에 포함되어 있습니다.

예를 들어, 입력 전압이 증가함에 따라 출력도 증가하여 트랜지스터 VT2의 베이스 전압이 증가하는 동시에 에미터 VT2의 전위는 동일하게 유지됩니다.이것은 기본 전류의 증가로 이어지고 따라서 트랜지스터 VT2의 콜렉터 전류 — 트랜지스터 VT1의 기본 전위가 감소하고 트랜지스터가 닫히고 더 큰 전압 강하가 발생하며 출력 전압이 바뀌지 않은 채로.

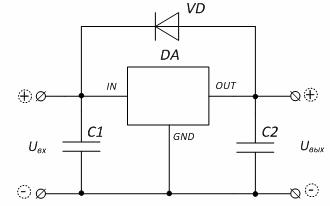

오늘날 스태빌라이저는 집적 회로 형태로 생산됩니다. 통합 스태빌라이저를 켜는 일반적인 방식이 그림 6에 나와 있습니다.

그림 6 - 내장형 전압 안정기를 켜는 일반적인 회로도

스태빌라이저 마이크로 회로의 출력 지정: «IN» — 입력, «OUT» — 출력, «GND» — 공통(케이스). 스태빌라이저를 조정할 수 있는 경우 출력 «ADJ» — 조정이 있습니다.

스태빌라이저의 선택은 출력 전압 값, 최대 부하 전류 및 입력 전압 변동 범위를 기준으로 합니다.